Here we come with a new post on synchronous counter. In my previous post I discussed on asynchronous counter. Now through this post we try to learn some very important topic which create lots of confusion.

- Asynchronous and synchronous counter.

- Single and multimode counters.

- Modulus counters.

- Why we use synchronous counter instead of asynchronous counter?

- Working principal of Synchronous Counter

Asynchronous and synchronous counter

The asynchronous counter is simple and straightforward in operation and construction and usually requires a minimum amount of hardware. In asynchronous counters, each flip-flop is triggered by the previous flip-flop, and hence the speed of operation is limited. In fact, the settling time of the counter is the cumulative sum of the individual settling times of the flip-flops. This type of counters is also called ripple or serial counter. And If all the flip-flops of a counter are clocked synchronously then this is known as a synchronous counter.

Single and multimode counters

The counters can be designed such that the contents of the counter advances by one with each clock pulse; and is said to operate in the count-up mode. The opposite is also possible, when the counter is said to operate in the count-down mode. In both cases the counter is said to be a single mode counter. If the same counter circuit can be operated in both the UP and DOWN modes, it is called a multimode counters.Modulus counters

Modulus counters are defined based on the number of states they are capable of counting. This type of counter can again be classified into two types: Mod N and MOD < N. For example, if there are n bits then the maximum number counted can be 2n or N. If the counter is so designed that it can count up to 2n or N states, it is called MOD N or MOD 2n counter. On the other hand, if the counter is designed to count sequences less than the maximum value attainable, it is called a MOD < N or MOD < 2n counter.Why we use synchronous counter instead of asynchronous counter?

If we think on the timing delay to perform an operation of counter then we will find each flip-flop has a specific delay time. In ripple counters these delay times are additive and the total “settling” time for the counter is approximately the product of the delay time of a single flip-flop and the total number of flip-flops.

Now if we want to overcome this problem we need something to do. And the solution is if all the flip-flops are clocked synchronously then we can easily overcome the problem. If all the flip-flops of a counter are clocked synchronously then this is known as a synchronous counter.

Working principal of Synchronous Counter

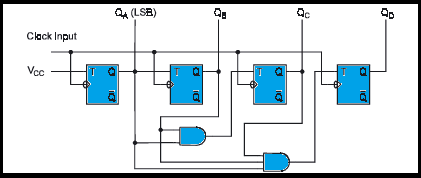

Synchronous counters can be designed for any count sequence (need not be straight binary). In bellow picture is shown of a simple 4-bit synchronous counter.

The above picture is shows A 4-bit synchronous counter with parallel carry. In carefully look that the clock inputs of all the flip-flops are tied together so that the input clock signal may be applied simultaneously to each flip-flop. As we see all flip-flops are T flip-flop and it work on toggle mode when T input is 1. That is why only the LSB flip-flop A has its T input connected permanently to logic 1 (i.e., VCC), while the T inputs of the other flip-flops are driven by some combination of flip-flop outputs. The T input of flip-flop B is connected to the output QA of flip-flop A; the T input of flip-flop C is connected with the AND-operated output of QA and QB. Similarly, the T input of D flip-flop is connected with the AND-operated output of QA, QB, and QC.

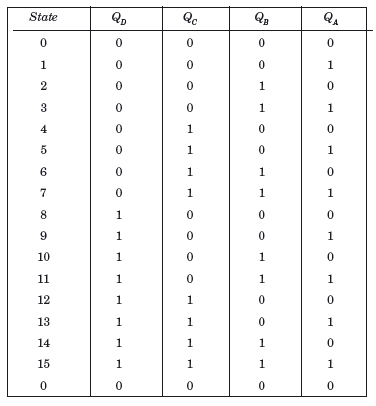

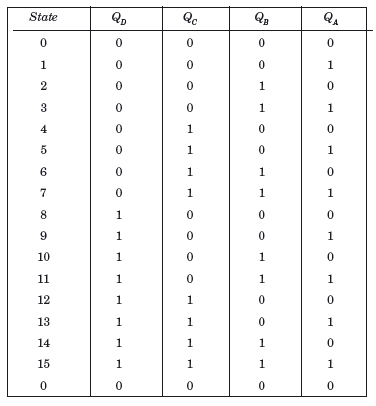

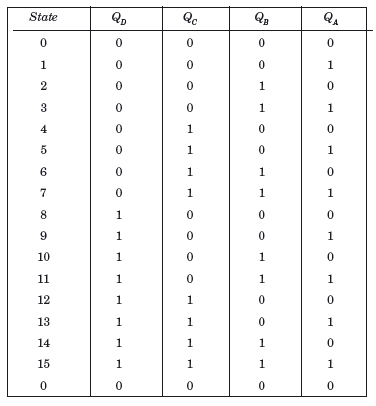

As we know a T flip-flop changes its state with the negative transition of each clock pulse for T is high. Flip-flop B changes its state only when the value of QA is 1 and a negative transition of the clock pulse takes place. Similarly, flip-flop C changes its state only when both QA and QB are 1 and a negative edge transition of the clock pulse takes place. In the same manner, the flip-flop D changes its state when QA = QB = QC = 1 and when there is a negative transition at clock input. The count sequence of the counter is given in Table

Let Check How you learn counter? with simple quiz.

Counter

Time limit: 0Quiz-summary

0 of 5 questions completed

Questions:

- 1

- 2

- 3

- 4

- 5

Information

Counter

You have already completed the quiz before. Hence you can not start it again.

Quiz is loading...

You must sign in or sign up to start the quiz.

You have to finish following quiz, to start this quiz:

Results

0 of 5 questions answered correctly

Time has elapsed

You have reached 0 of 0 points, (0)

Average score Your score

Categories

- Not categorized 0%

- 1

- 2

- 3

- 4

- 5

- Answered

- Review

- Question 1 of 5

1. Question

A ring counter with 5 flip flops will have …… states.

-

-

-

-

Correct

Incorrect

- Question 2 of 5

2. Question

Ripple counters are also called ____________

-

-

-

-

Correct

Incorrect

- Question 3 of 5

3. Question

How many types of the counter are there?

-

-

-

-

Correct

Incorrect

- Question 4 of 5

4. Question

A counter circuit is usually constructed of ____________

-

-

-

-

Correct

Incorrect

- Question 5 of 5

5. Question

In a ripple counter,

-

-

-

-

Correct

Incorrect