To know the working of 8085 microprocessor, we should know the timing diagram of 8085 microprocessor. With help of timing diagram, we can easily calculate the execution time of instruction and as well as program. Before going for timing diagram of 8085 microprocessor, we should know some basic parameters to draw timing diagram of 8085 microprocessor. Those parameters are

- Instruction Cycle

- Machine cycle

- T-state.

Parameters of Timing Diagram

Now we should go for what is instruction cycle, machine cycle and t-state?

Instruction Cycle

Instruction cycle is the total time taken for completing one instruction execution

Machine cycle

Machine cycle is the time required to complete one operation such as accessing either the memory or an I/O device

T-state

T-state is the time corresponding to one clock period. It is a basic unit. It used to calculate the time taken for execution of instructions and programs in a processor.

Now another important topics we should know to clear the concept on timing diagram of 8085 microprocessor. What are the control signals uses in timing diagram of 8085 microprocessor?

Control Signal

If we go for above question then the answer is mainly we have to know five control signal to understand timing diagram of 8085 microprocessor. Those are

IO/ M

IO/ M signal indicate whether I/O or memory operation carried out. A high on this signal indicates I/O operation while a low indicates memory operation.

S0 and S1

S0 and S1 indicate the type of machine cycle in progress.

ALE

ALE is indicates the availability of a valid address on the multiplexed address/data lines. When it is high act as a address bus and low act as a data bus.

Rd^

Read is an active low signal. It indicates that data has to read form the selected memory or i/o device through data bus.

WR^

Write is an active low signal that indicates that data on the data bus is to be write form the selected memory or i/o device.

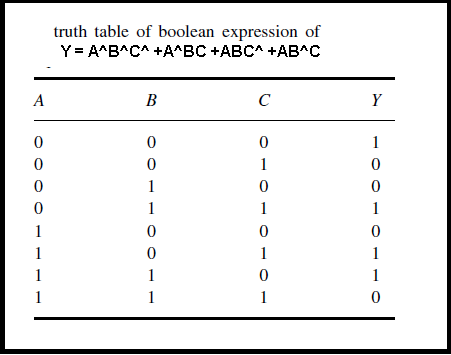

In bellow table I show the status of different control signal for different operation. We should remember that to complete our timing diagram of 8085 microprocessor.

Now in bellow diagram see the opcode fetch timing diagram.

Opcode Fetch

The lower byte of address (AD0 – AD7) is available on the multiplexed address/data bus during T1 state of each machine cycle, except during the bus idle machine cycle.

The higher byte of address (A8 – A15) is available during T1 to T3 states of each machine cycle, except during the bus idle machine cycle, shown in Fig

The first machine cycle of every instruction is the Opcode Fetch. This indicates the kind of instruction to be executed by the system. The length of this machine cycle varies between 4T to 6T states—it depends on the type of instruction. In this, the processor places the contents of the PC on the address lines, identifies the nature of machine cycle æ (by IO/M, S0, S1) and activates the ALE signal. All these occur in T1 State In T2 state, RD signal is activated so that the identified memory location is read from and places the content on the data bus (D0 – D7 ).

In T3, data on the data bus is put into the instruction register (IR) and also raises the RD^ signal thereby disabling the memory.

In T4, the processor takes the decision, on the basis of decoding the IR, whether to enter into T5 and T6 or to enter T1 of the next machine cycle.

One byte instructions that operate on eight bit data executed in T4. Examples are ADD B, MOV C, B, RRC, DCR C,etc.

Example

Now see an example of memory read and memory write machine cycle.

Both the Memory Read and Memory Write machine cycles are 3T states in length. In Memory Read the contents of R/W memory (including stack also) or ROM are read while in Memory Write, it stores data into data memory.

As is evident from Fig during T2 and T3 states data from either memory or CPU are made available in Memory Read or Memory Write machine cycles respectively. The status signal (IO/ M, S0, S1) states are complementary in nature in Memory Read and Memory Write cycles. Reading or writing operations mainly performed in T2 cycle.

In T3 of Memory Read, data from data bus are placed into the specified register (A,B, C, etc.). After that it raises RD so that memory will disabled. While in T3 of Memory Write, WR^ signal raised for disabling the memory.

Let’s check how you learn “Timing diagram of 8085 microprocessor” with a simple quiz.

0 of 5 questions completed Questions: Architecture of 8085 microprocessor You have already completed the quiz before. Hence you can not start it again. Quiz is loading... You must sign in or sign up to start the quiz. You have to finish following quiz, to start this quiz: 0 of 5 questions answered correctly Time has elapsed You have reached 0 of 0 points, (0) Which is not the control bus signal: Name of typical dedicated register is: The cycle required to fetch and execute an instruction in a 8085 microprocessor is which one of the following? Which of the following statements for Intel 8085 is correct? ALU (Arithmetic and Logic Unit ) of 8085 microprocessor consists of8085 Architecture

Quiz-summary

Information

Results

Average score Your score Categories

1. Question

2. Question

3. Question

4. Question

5. Question

1 thought on “Timing diagram of 8085 microprocessor”

in io/M M should be M^