Here we see how interrupt driven I/O data transfer work. In my previous post I discussed on programmed I/O data transfer method. And we saw that in the programmed I/O data transfer method, microprocessor is busy for all the time. Because in this mode, it always checking for the availability of data from the slower I/O devices. And it also busy in checking if I/O device is ready for the data transfer or not. In other words, in this data transfer scheme, some of the microprocessor time is wasted in waiting while an I/O device is getting ready. To overcome this problem interrupt driven I/O data transfer introduced.

Introduction

The interrupt driven I/O data transfer method is very efficient. Because no microprocessor time is wasted in waiting for an I/O device to be ready. After checking the I/O device is ready or not. In this interrupt driven I/O data transfer method, the I/O device informs the microprocessor for the data transfer. And This can achieved by interrupting the microprocessor. As we know, the interrupt is hardware facilities provided on the microprocessor.

Working Process

Now come to the working process of interrupt driven I/O data transfer. So the beginning, the microprocessor requesting the I/O device ‘to get ready’. After that it initiates data transfer. In between this time frame, it continue executing its original program rather wasting its time by checking the status of I/O device. Whenever the device is ready to accept or supply data. It send information to the processor through a control signal. This control signal is known as interrupt (INTR) signal.

First step, in response to this interrupt signal, the microprocessor sends back an interrupt acknowledge signal to the I/O device. By sending acknowledgement, it indicating that it received the request.

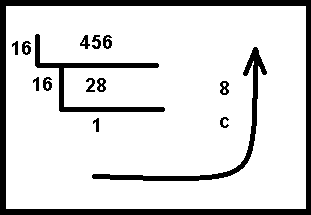

Second step, then it suspends its job after executing the current instruction. It saves the contents and status of program counter to stack. And it jumps to the subroutine program.

This subroutine program is called Interrupt Service Subroutine (ISS) program. The ISS stores the status of processor into stack. After that, it start executing the instruction for the data transfer. Finally, it restores the processor status and then returns back to main program.

Complete process in easy steps

So in short, we just point out those steps with quick recall.

- A peripheral device send an interrupt request.

- Processor complete the execution of the current instruction.

- Now the processor issued an acknowledgement request.

- The program then branches to Interrupt Service Subroutine (ISS) program.

- The return address is stored in the stack.

- Stored other register contents as per program needs.

- Data transfer takes place under ISS.

- Enabled the interrupt system.

- Loading the return address from stack into program counter (PC).

- The program then returns to the main program.

Configuration

Using interrupt driven data transfer scheme, several input/output devices may connected to microprocessor. Following interrupt request configuration may arise while interfacing the I/O devices to microprocessor.

- Single Interrupt system.

- Multi Interrupt System.

Single Interrupt System

When only one interrupt line is available with the microprocessor. And several I/O devices has to connect. Then the method will known as Single Interrupt System.

Multi Interrupt System

When the microprocessor has several interrupt terminals. And one I/O device has to connect in each interrupt terminal. Then it known as multi interrupt system. Now some important thing we should remember. In this scheme, the number of I/O devices to be connected to the interrupt lines should be equal to or less than the number of interrupt terminals. In this way one device can connected to each level of interrupt. So when a device interrupts the microprocessor, it immediately knows which device has interrupted. Such an interrupt scheme also known as vectored interrupt.

Let’s check how you learn interrupt driven I/O data transfer with a simple quiz.

0 of 5 questions completed Questions: Data Transfer in 8085 microprocessor. You have already completed the quiz before. Hence you can not start it again. Quiz is loading... You must sign in or sign up to start the quiz. You have to finish following quiz, to start this quiz: 0 of 5 questions answered correctly Time has elapsed You have reached 0 of 0 points, (0) The control signal used to distinguish between an I/O operation and memory operation is The stack and the stack pointer The total I/O space available in 8085 if used peripheral mapped I/O The interfacing device used with an output port is In 8085 CPU, the JUMP instruction address affects theData Transfer

Quiz-summary

Information

Results

Average score Your score Categories

1. Question

2. Question

3. Question

4. Question

5. Question