Masking of Interrupts in 8085 microprocessor is most important portion of interrupt. In 8085 microprocessor masking of interrupt we can do for four hardware interrupts INTR, RST 5.5, RST 6.5, and RST 7.5. The masking of 8085 interrupts, we can do at different levels. In bellow figure shows the organization of hardware interrupts in the 8085 microprocessor.

- The maskable interrupts by default masked by the Reset signal. So no interrupt recognized by the hardware reset.

- The interrupts can enabled by the EI instruction.

- The three RST interrupts can selectively masked by loading the appropriate word in the accumulator and executing SIM instruction. This iscalled software masking.

- All maskable interrupts disabled whenever an interrupt recognized.

- All maskable interrupts can disabled by executing the DI instruction.

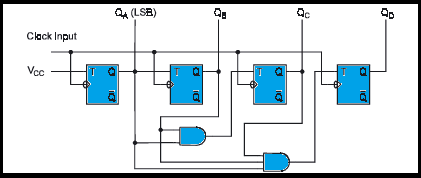

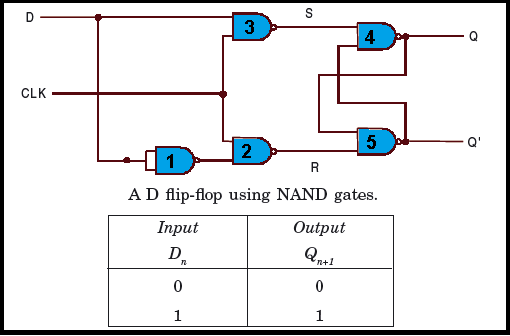

If we talk about RST 7.5 interrupt. It alone has a flip-flop to recognize edge transition. The DI instruction reset interrupt enable flip-flop in the processor and the interrupts disabled automatically. To enable interrupts, EI instruction has to be executed.

SIM Instruction:

The SIM instruction generally used to mask or unmask RST hardware interrupts. When it executed, the SIM instruction reads the content of accumulator and accordingly mask or unmask the interrupts. The format of control word to be stored in the accumulator before executing SIM instruction shown in Fig. 2.

In addition to masking interrupts, SIM instruction can used to send serial data on the SOD line of the processor. Now need to send the data. So it placed in the MSB bit of the accumulator. And finally the serial data output enabled by making D6 bit to 1.

RIM Instruction:

RIM instruction is used to read the status of the interrupt mask bits. So when RIM instruction is executed. The accumulator then loaded with the current status of the interrupt masks and the pending interrupts also. The format and the meaning of the data stored in the accumulator after execution of RIM instruction shown in Fig. 3.

In addition RIM instruction is used to read the serial data on the SID pin of the processor. The data on the SID pin then stored in the MSB of the accumulator after the execution of the RIM instruction.

Ex: Write an assembly language program to enables all the interrupts in 8085.

- After reset.

- EI : Enable interrupts

- MVI A, 08H : Unmask the interrupts

- SIM : Set the mask and unmask using SIM instruction.

Hope the above discussion clear your concept regarding Masking of Interrupts in 8085 microprocessor

Let’s check how you learn Masking of Interrupts in 8085 microprocessor with a simple quiz.

0 of 5 questions completed Questions: Interrupt of 8085 microprocessor You have already completed the quiz before. Hence you can not start it again. Quiz is loading... You must sign in or sign up to start the quiz. You have to finish following quiz, to start this quiz: 0 of 5 questions answered correctly Time has elapsed You have reached 0 of 0 points, (0) Which interrupt has the highest priority? What are level Triggering interrupts? What are software interrupts? What is SIM? What is meant by Maskable interrupts?interrupt

Quiz-summary

Information

Results

Average score Your score Categories

1. Question

2. Question

3. Question

4. Question

5. Question